# Review of Low Power and High Speed Implementation of 3-bit Flash Analog to Digital Converter

C. Vivek, S. Palanivel Rajan\*

Department of Electronics and Communication Engineering, M. Kumarasamy College of Engineering, Karur, Tamil Nadu, India.

\*Corresponding author: E-Mail: palanivelrajanme@gmail.com ABSTRACT

In this paper, we present High speed and Low power implementation of 3-bit flash analog to digital converter. Analog to Digital converter is a device which converts continuous physical quantity to digital quantity. In the current CMOS technology power reduction is the foremost question at daily vitality. In advanced area, power utilization and low voltage form into wide component which is strenuous for disregard converters and high speed devices. In this paper by using diode based stacked power gating technique and low leakage stacked power gating technique a complete inquisition of 3-bit flash ADC circuit is proposed. These power gating method reduce the average power and the leakage current efficiently. The important criteria to effect the efficiency of data conversion systems are speed, resolution and power consumption. Simulation has been performed using cadence virtuoso tool at assorted power supply by 90nm technology to evaluate the power gating techniques.

**KEY WORDS:** Leakage Current, Stacked Power Gating Technique, 3-Bit Flash ADC, Power.

## 1. INTRODUCTION

This 3-bit flash ADC is a device which converts Analog form to digital form. This 3-bit flash ADC device otherwise known as parallel ADC. 2<sup>N</sup>-1 comparators are used in N-bit converter ADC circuit, where N equals to 3. In this present scenario system-on-chip flourish more; so signal processing component utilization is a most important factor. It is having high speed in GIGA sample and power consumption in mW. In this 3-bit flash ADC comparator plays a prominent role. To compare two signals a comparator is a needed device in ADC. In this paper differential based comparator is used which is having high frequency.

Encoder is a part which is used in flash ADC, it locates besides the comparator this sleep transistor is placed in between circuit ground and actual ground. Power utilization, resolution and speed can be the important factor for some data conversion system efficiency. This complete inspect has simulated in cadence tool in GPDK 90nm CMOS technology using supply voltage as 1.2V.

### Background:

# **Explaining the blocks present in 3-bit flash ADC:**

**Comparator:** There are different types of comparators. Some of them are discussed below. Showing different comparators in the below table with respective to their supply voltage and power consumption.

**Table.1. Different types of comparator**

| Comparators               | Supply voltage | Power consumption |

|---------------------------|----------------|-------------------|

| OPAMP based               | 1.2V           | 52.80 mw          |

| Differential comparator   | 1.2V           | 49.94mw           |

| Double tail               | 1.2V           | 0.006mw           |

| Dynamic latched           | 1.2V           | 0.003mw           |

| Current mode saturation   | 1.2V           | 0.6mw             |

| Current mode subthreshold | 1.2V           | 114.2mw           |

In this paper used differential comparator. Comparator is a device which compares two input signals and gives output as digital signal. It have two analog input terminals V+ and V- and output Vo.

$$V0 = \begin{cases} 1, & \text{If } V+>V-\\ 0, & \text{If } V+< V- \end{cases}$$

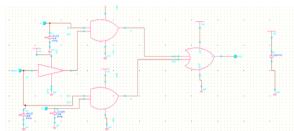

Figure.1. Symbol for comparator

Comparator was designed with input DC voltage 0.6V and VDD as 1.2V. This comparator will be applicable up to 6GHZ. Done outputs with transient and DC analysis.

**Encoder:** Encoder can be designed in many ways using gates. There are different types of Encoder. Some of them are explained below. Showing different Encoders in the below table with respective to their delay, power, and their advantages.

Figure.2. Schematic of comparator Table.2. Comparison of different Encoder

| Tubicizi Computison of unferent Encoder |                     |                                               |                          |                 |  |

|-----------------------------------------|---------------------|-----------------------------------------------|--------------------------|-----------------|--|

|                                         | Rom based encoder   | der   Wallace tree encoder   Fat tree encoder |                          | Mux based       |  |

|                                         |                     |                                               |                          | encoder         |  |

| Delay (ns)                              | 0.1346              | 4.05                                          | 0.09343                  | 0.1325          |  |

| Power (u wat)                           | 431.8               | 8.27                                          | 0.1104                   | 0.0442          |  |

| Advantage                               | Contain an in       | Offer global error                            | Thermometer 2:1 to In    | High speed, low |  |

|                                         | encoder portion and | correction consists of                        | conde then into binary,  | power           |  |

|                                         | thermometer 2:1 hot | full adder in encoder                         | implement using XOR      | consumption,    |  |

|                                         | code then into      | portion                                       | and XNOR in encoder      | low circuit     |  |

|                                         | binary, simple      |                                               | portion. Faster than ROM | complexity      |  |

|                                         | desing              |                                               | based                    |                 |  |

| Disadvantage                            | Slow speed, larger  | Latency problem, high                         | Slow and more            |                 |  |

|                                         | power consumption,  | routing complexity                            | consumption              |                 |  |

|                                         | bubble error        |                                               | -                        |                 |  |

Now here we can see that Encoder also is current mode which is basically to attain high speed in this complete work we have simulated three different type of Encoder and on the basis of that we can say that MUX based Encoder is fastest and less power consuming and in MUX based Encoder we can simulate for three different topology which are as follows

- Implementation of 2:1 multiplexer using basic gate

- Implementation of 2:1 multiplexer using transmission gate

- Implementation of 2:1 multiplexer using current mode logic multiplexer.

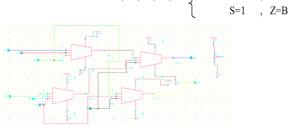

In this paper we used 2:1 multiplexer using basic gate. The schematic of the 2:1 multiplexer using basic gate can be designed by using AND, OR and NOT gates .Whereas 2 AND gates, 1 OR gate and 1 NOT gate. Hence schematic was shown below.

Figure.3. 2:1 MUX using basic gates

First designing AND, NOR and NOT gates using CMOS technology in the gpdk90nm and creating symbol for that and forming 2:1MUX. This MUX was designed with VDD=1.2, DC voltage as 1.2. MUX formula shown below.

Where S=0 , Z=A

Figure.4. 8:3 Encoder using MUX

8:3 Encoder is designed with MUX. Using stimuli procedure and giving VDD as 1.2V and done simulation in cadence and creating symbol for the 8:3 Encoder.

**BIT FLASH ADC:** Different types of flash ADC are discussed below:

Table.3. Comparison of different ADC

|              | Flash ADC                       | SAR ADC                                                                                                                     | Pipeline ADC                                                                                 | Integrating ADC                                                                                                                                                          | Sigma delta<br>ADC                                                          |

|--------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Advantage    | High speed<br>in giga<br>sample | Medium resolution 8- 16 bit, speed in mega sample, low power and small size, less expensive and determine one bit at a time | Resolution<br>between 8-14 bits,<br>speed 100Mbps,<br>low power<br>consumption than<br>flash | Use in monitoring of DC signal, in industrial and DC signal, high resolution around 16bit, less expensive, less power consumption, good noise performance, speed 100Mbps | High resolution<br>12-24 bit, lower<br>bandwidth                            |

| Disadvantage | Power consumption in milli watt | Speed less 5<br>Mbps                                                                                                        | Latency                                                                                      |                                                                                                                                                                          | Not applicable<br>for<br>multichannel,<br>require filter to<br>remove noise |

Flash ADC Architecture:

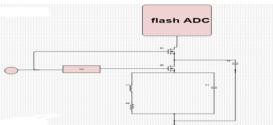

**Flash ADC:** Flash ADC architecture is shown below which is designed and implemented in gpdk90 nm CMOS technology. 3-bit flash ADC is a circuit which consists of  $2^{N}$ -1 comparators, where N=3.  $2^{3}$  -1 = 7 so using 7 comparators.

Table.4. Comparison of different ADC

|               | Table.4. Comparison of different ADC |                    |                        |                   |                               |  |  |

|---------------|--------------------------------------|--------------------|------------------------|-------------------|-------------------------------|--|--|

| Conversion    | N bits 2 <sup>N</sup> -1             | Binary search      | Unknown input          | Small parallel    | Oversampling                  |  |  |

| method        | comparators                          | algorithm,         | voltage is             | structure, each   | ADC, 5-HZ to 60               |  |  |

|               |                                      | internal circuitry | integrated and         | stage works on    | HZ rejection                  |  |  |

|               |                                      | runs higher speed  | value compared         | one to a few bits | programmable                  |  |  |

|               |                                      |                    | against known          |                   | data output                   |  |  |

|               |                                      |                    | reference value        |                   |                               |  |  |

| Encoding      | Thermometer                          | Successive         | Analog                 | Digital           | Over sampling                 |  |  |

| method        | code encoding                        | approximation      | integration            | correction logic  | modulator, digital            |  |  |

|               |                                      |                    |                        |                   | decimation filter             |  |  |

| Disadvantages | Sparkle codes,                       | Speed limited to   | Slow                   | Parallelism       | Higher order (4 <sup>th</sup> |  |  |

|               | met stability,                       | 5Mbps may          | conversion rate.       | increases         | order or higher) –            |  |  |

|               | high power                           | require anti-      | High precision         | throughput at     | multibit ADC and              |  |  |

|               | consumption,                         | aliasing filter    | external               | the expense of    | multibit feedback             |  |  |

|               | large size,                          |                    | components             | power and         | DAC                           |  |  |

|               | expensive                            |                    | required to achieve    | latency           |                               |  |  |

|               |                                      |                    |                        |                   |                               |  |  |

| Conversion    | Conversion time                      | Increases linearly | accuracy<br>Conversion | Increase linearly | Trade-off                     |  |  |

| time          | does not change                      | with increased     | time doubles           | with increased    | between data                  |  |  |

| time          | with increased                       | resolution         | with every bit         | resolution        | output rate and               |  |  |

|               | resolution                           | resolution         | increase in            | resolution        | noise free                    |  |  |

|               | 10501441011                          |                    | resolution             |                   | resolution                    |  |  |

| Resolution    | Component                            | Component          | Component              | Component         | Component                     |  |  |

|               | matching                             | matching           | matching does          | matching          | matching                      |  |  |

|               | typically limits                     | requirements       | not increase           | requirements      | requirements                  |  |  |

|               | resolution to 8                      | double with every  | with increase in       | double with       | double with every             |  |  |

|               | bits                                 | bit increases in   | resolution             | every bit         | bit increase in               |  |  |

|               |                                      | resolution         |                        | increase in       | resolution                    |  |  |

|               |                                      |                    |                        | resolution        |                               |  |  |

| Size          | 2 <sup>N</sup> -1                    | Die increases      | Core die size          | Die increases     | Core die size will            |  |  |

|               | comparators, die                     | linearly with      | will not               | linear with       | not materially                |  |  |

|               | size and power                       | increase in        | materially             | increase in       | change with                   |  |  |

|               | increases                            | resolution         | change with            | resolution        | increase in                   |  |  |

|               | exponentially                        |                    | increase in            |                   | resolution                    |  |  |

|               | with resolution                      |                    | resolution             |                   |                               |  |  |

Figure.5. Schematic of 3-bit flash ADC

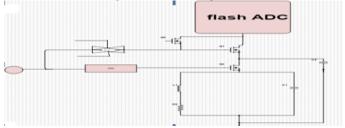

**Stacked power gating technique:** Below figure shows the stacked power gating technique used in flash ADC. In this technique sleep transistors are used, by using these transistors leakage current may reduce. Here ST1 and ST2 are the sleep transistors. ST1 and ST2 will be off in standby mode; hence in this condition leakage current may reduce.

While doing simulation we will observe 3 modes.

**Active mode:** Both ST1 and ST2 will be staying in ON condition i.e., sleep transistor remains at logic 1. In this mode both transistors may have low resistance.

Voltage across C1 = VC1 (active mode) =V(R1ON) + (R2ON)

Voltage across C2 = VC2 (active mode) =V (R2ON) = 0V

**Standby mode:** Both ST1 & ST2 are off on standby mode and both offers high resistance. Capacitance C1 charges up to voltage V1 and capacitance C2 charges up to voltage V2. So, VC1 (Standby mode) = V1, VC2 (Standby mode) = V2

**Sleep to active mode transition:** In this sleep transistor will be off. Control signal will be in on condition. The parameters T1 and capacitances C2 will keep to particular value that is based on following factors: Minimum ground bounce noise, Minimum leakage current.

Figure.6. Schematic of stacked power gating

# Diode based stacked power gating technique:

- Transistor M1 and M2 are sleep transistors. For less leakage current these transistors use high threshold voltage.

- To make sleep transistor M1 functioning as diode during mode transition T1 is used as control transistor.

Figure.7. Diode based power gating technique

**Modification of this project:** In the given paper the circuit will be applicable up to 1GHZ hence by modifying the comparator the circuit will be applicable more than 1GHZ. Hence these type of circuits may use in different applications.

Modified comparator is shown below;

Design parameters of the circuit is Technology library: gpdk 90nm, Supply voltage: 1.2V, Length: 100nm, Width: according to their sizing

# 2. CONCLUSION

Flash ADC topology is nothing but fastest ADC topology, by using higher bandwidth flash ADC will increase speed and power dissipation is increases exponentially. If circuit contains high speed and power dissipation can use in different applications, hence this project used in Ultra-Wide Band application.

Hence shown Designing and implementing the circuit of 3-bit Analog to Digital, whereas by using power gating technique to the flash ADC for reducing leakage current and average power. Designing and implementing the circuit of 3-bit Analog to Digital by using power gating technique to the flash ADC for reducing leakage current and average power. Hence these techniques are going to design in gpdk45 nm technology.

# Journal of Chemical and Pharmaceutical Sciences

#### REFERENCES

Bailey D, Soenen E, Gupta P, Villarrubia P and Sang D, Challenges at 45 nm and beyond, IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2008, 11-18.

Chen C.Y, Le M and Kim K.Y, A low power 6-bit flash ADC with reference voltage and common-mode calibration, in Symp. VLSI Circuits Dig, 2008, 12–13.

Guopu Zhu & Sam Kwong, G best guided artificial bee colony algorithm for numerical function optimization, Applied Mathematics and Computation, 217, 2010, 3166-3173.

Jiao H and Kursun V, Noise, Aware Data Preserving Sequential MTCMOS Circuits with Dynamic Forward Body Bias, Journal of Circuits, Systems and Computers, 20 (1), 2011, 125-145.

Juliana dos Santos B, Carlos Heuser A, Viviane Moreira P and Leandro Wives K, Automatic threshold estimation for data matching applications, Information Sciences, 181 (13), 2011, 2685-2699.

Meher M.R, Jong C.C and Chip-Hong Chang, A High Bit Rate Serial-Serial Multiplier with On-the-Fly Accumulation by Asynchronous Counters, IEEE Trans. On Very Large Scale Integr. (VLSI) System, 19 (10), 2011, 1733-1745.

Palanivel Rajan S, Sukanesh R, Experimental Studies on Intelligent, Wearable and Automated Wireless Mobile Tele-Alert System for Continuous Cardiac Surveillance, Journal of Applied Research and Technology, 11 (1), 2013, 133 – 143.

Park J.C and Mooney V.J, Sleepy Stack Leakage Reduction, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 14 (11), 2006, 1250-1263.

Shriram Vasudevan K, Vivek C, An Intelligent Attempt to Export Files into Cloud in Handheld Devices through Gesture Recognition, Indian Journal of Science and Technology, 8, 2015, 1-8.

Singh H, Agarwal K, Sylvester D and Nowka K.J, Enhanced Leakage Reduction Techniques Using Intermediate Strength Power Gating, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 15 (11) 2007, 1215-1224.

Stojcevski A, Le H.P, Zayegh A and Singh J, Flash ADC Architecture, IEEE Electronic Letters Journal, 2003.

Suhwan Kim, Chang Jun Choi, Deog-Kyoon Jeong, Kosonocky S.V and Sung Bae Park, Reducing Ground-Bounce Noise and Stabilizing the Data-Retention Voltage of Power-Gating Structures, IEEE Transactions on Electron Devices, 55 (1), 2008, 197-205.

Sukanesh R, Palanivel Rajan S, Cellular Phone based Biomedical System for Health Care, Proceedings of the IEEE, International Conference on Communication Control and Computing Technologies, INSPEC Accession Number, 11745436, 2010, 550-553.

Sundstrom T and Alvandpour A, Utilizing process variations for reference generation in a flash ADC, IEEE Trans. Circuits Syst. II, Exp. Briefs, 56 (5), 2009, 364–368.

Temes G, Micropower data converters, A tutorial, IEEE Trans. Circuits Syst II, Exp Briefs, 57 (6), 2010, 405–410.

Uyttenhove K and Steyaert M, A 1.8 V 6-bit 1.3 GHz flash ADC in 0.25 m CMOS, IEEE J. Solid-State Circuits, 38 (7), 2003, 1115–1122.

Vijayprasath S, Palanivel Rajan S, Performance Investigation of an Implicit Instrumentation Tool for Deadened Patients Using Common Eye Developments as a Paradigm, International Journal of Applied Engineering Research, 10 (1), 2015, 925-929.

Vivek C, Palanivel Rajan S, Z-TCAM, An Efficient Memory Architecture Based TCAM, Asian Journal of Information Technology, 15 (3), 2016, 448-454.

Wang Z and Chang M.C.F, A 1-V 1.25-GS/S 8-bit self-calibrated flash ADC in 90-nm digital CMOS, IEEE Tran. Circuits Syst II, Exp Briefs, 55 (7), 2008, 668–672.

Wang Z and Chang M.C.F, A 600-MSPS 8-bit CMOS ADC using distributed track-and-hold with complementary resistor/capacitor averaging, IEEE Trans. Circuits Syst I, Reg Papers, 55 (11), 2008, 3621–3627.

Weaver S, Hershberg B, Kurahashi P, Knierim D and Moon U, Stochastic flash analog-to-digital conversion, IEEE Trans. Circuits Syst I, Reg, 57 (11), 2010, 2825–2833.

Wong Y.L, Cohen M.H and Abshire P.A, A 750- MHz 6-b adaptive floating-gatequantizer in 0.35-μm CMOS, IEEE Trans. Circuits Syst I, Reg, 56 (7), 2009, 1301–1312.